01

先进封装行业概览

封装是指将生产加工后的晶圆进行切割、焊线塑封,使电路与外部器件实现连接,并为半导体产品提供机械保护,使其免受物理、化学等环境因素损失的工艺。

随着半导体先进制程不断往7nm/5nm,甚至以下迈进,晶片设计与制造工艺微缩的难度、成本与开发时间均呈现跳跃式的增长。

面对此难题,晶片业者试图透过先进封装来达到晶片间的高密度互联,以实现以更低成本提供同等级效能表现。

先进封装采用了先进的设计思路和先进的集成工艺,对芯片进行封装级重构,并且能有效提升系统高功能密度的封装技术。

先进封装工艺包括倒装焊(FlipChip)、晶圆级封装(WLP)、2.5D封装(Interposer) 、3D封装 (TSV)、Chiplet等。

据 Yole 数据,2021 年全球封装市场规模约达 777 亿美元。其中,先进封装全球市场规模约 350 亿美元。

预计到 2025年先进封装的全球市场规模将达到 420 亿美元,2019-2025 年全球先进封装市场的 CAGR 约 8%。

相比同期整体封装市场 (CAGR=5%)和传统封装市场,先进封装市场增速更为显著。

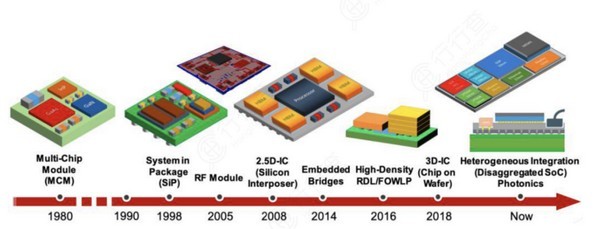

芯片整合已演进至2.5D/3D及Chiplet封装:

资料来源:Cadence

02

Chiplet 行业概览

随着半导体制程节点的持续演进,短沟道效应以及量子隧穿效应带来的发热、漏电等问题愈发严重,追求经济效能的摩尔定律日趋放缓。

在此背景下,产业开始思考将不同工艺的模块化芯片。

Chiplet又称芯粒或小芯片,是先进封装技术的代表,将复杂芯片拆解成一组具有单独功能的小芯片单元 die(裸片),通过 die-to-die 将模块芯片和底层基础芯片封装组合在一起。

Chiplet 实现原理与搭积木相仿,从设计时就按照不同的计算单元或功能单元对其进行分解,然后每个单元选择最适合的工艺制程进行制造,再将这些模块化的裸片互联起来,通过先进封装技术,将不同功能、不同工艺制造的Chiplet封装成一个系统芯片,以实现一种新形式的 IP 复用。

Chiplet 的概念源于 Marvell 创始人周秀文博士在 ISSCC 2015 上提出的 Mochi(Modular Chip,模块化芯片)架构,伴随着 AMD 第一个将小芯片架构引入其最初的 Epyc 处理器 Naples,Chiplet 技术快速发展。

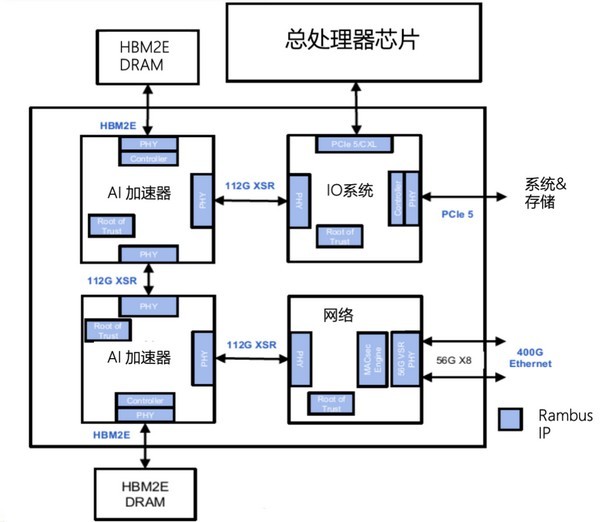

基于Chiplet 的异构架构应用处理器:

通过Chiplet技术,使用10nm工艺制造出来的芯片,完全也可以达到7nm芯片的集成度,但是研发投入和一次性生产投入则比7nm芯片的投入要少的多,新的连接形式在其生产过程中带动设备需求。

Chiplets结构:

资料来源:Omdia,Rambus,方正证券

Chiplet模式具备开发周期短、设计灵活性强、设计成本低和良率高等优点。可将不同工艺节点、材质、功能、供应商的具有特定功能的商业化裸片集中封装。

其作用主要包括:降低单片晶圆集成工艺良率风险,达到成本可控,有设计弹性,可实现芯片定制化;Chiplet将大尺寸的多核心的设计,分散到较小的小芯片,更能满足现今高效能运算处理器的需求;弹性的设计方式不仅提升灵活性,且可实现包括模块组装、芯片网络、异构系统与元件集成四个方面的功能。

资料来源:来源:CEIA电子制造

03

Chiplet 市场格局

目前Chiplet已经有少量商业应用,并吸引英特尔和AMD等国际芯片厂商投入相关研发,在当前SoC遭遇工艺节点和成本瓶颈的情况下有望发展成为一种新的芯片生态。

随着 Chiplet 逐步发展,未来来自不同厂商的芯粒之间的互联需求持续提升。

2022年3月,Chiplet的高速互联标准——UCIe(UniversalChiplet Interconnect Express,通用芯粒互联技术)正式推出,旨在芯片封装层面确立互联 互通的统一标准,打造一个开放 性的 Chiplet 生态系统。在解决Chiplet 标准化方面具有划时代意义。

UCIe联盟为Chiplet制定了多种先进封装技术,包括英特尔EMIB、台积电CoWoS、日月光FoCoS-B等。

UCle发起人为 Intel、AMD、ARM、高通、三星、台 积电、日月光、Google Cloud、Meta 和微软等十家公司。

UCIe联盟致力于推行Chiplet互联规范,当前联盟成员包括Synopsys、Cadence、ADI、博通等国际龙头。

对于中国半导体而言,后摩尔时代 Chiplet 是中国与国外技术差距相对较小的封装技术领域。

国内企业紧跟产业趋势,积极参与融入UCIe大生态,有望在Chiplet行业技术上乘势而上,实现突破。

国内企业中,芯原微电子、超摩科技、芯和半导体、芯耀辉、摩尔精英、灿芯半导体、忆芯科 技、芯耀辉、牛芯半导体、芯云凌、长鑫存储、超摩科技、希姆计算、世芯电子、阿里巴巴、OPPO、爱普科技、芯动科技、蓝洋智能等多家国内企业已成为 UCIe 联盟成员。

资料来源:UCle、招商证券

Chiplet开启了IP新型复用模式图片

Chiplet的实现开启了IP的新型复用模式,即硅片级别的IP复用。

不同功能的IP,如CPU、存储器、模拟接口等,可灵活选择不同的工艺分别进行生产,从而可以灵活平衡计算性能与成本,实现功能模块的最优配置而不必受限于晶圆厂工艺。

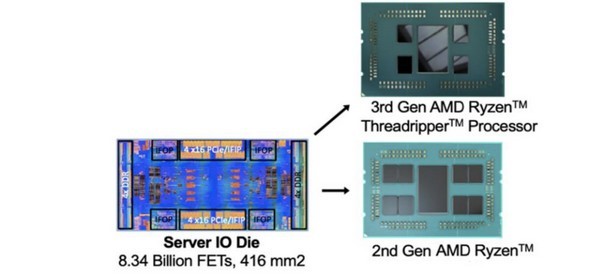

AMD 公司是第一个引入小芯片架构的供应商。AMD 在第三代锐龙(Ryzen)处理器上复 用了第二代霄龙(EPYC)处理器的 IO Chiplet,这种复用不但可以将“老旧制程”生 产的 Chiplet 继续应用到下一代产品中以节约成本,更能极大地节约设计、验证和生 产周期并降低失败风险。

AMD IO Chiplet 的复用:

就Chiplet和半导体IP的联系而言,Chiplet可以被看作是半导体IP经过设计和制程优化后的硬件化产品,其业务形成也从半导体IP的软件形式转向到Chiplet的硬件形式。

半导体IP的市场参与者可大致分为两类:新思科技和Cadence是与EDA工具捆绑型的半导体IP供应商,生态链优势明显;其余是在细分领域提供专业的IP核厂商。

当前IP市场仍然被英美国家高度垄断,全球前3厂商是Arm(英国)、Synopsys(美国)和Cadence(美国)。SST凭借着嵌入式非挥发性存储器异军突起,现在已经排到了全球第四。

国内芯原股份在全球前七名半导体IP授权供应商中,IP种类的齐备程度也具有较强竞争力。芯原股份是国内领先的一站式芯片定制服务和半导体 IP 授权服务的企业,利用 Chiplet 技术进行 IP 芯片化,有望给公司带来全新商业模式。

国内产业链相关厂商也在积极布局。

通富微电在先进封装方面公司已大规模生产 Chiplet 产品,7nm 产品已大规模量产,5nm 产品已完成研发即将量产。长电科技是国内封装 测试龙头企业,重点发展系统级(SiP)、晶圆级和 2.5D/3D 等先进封装 技术,并实现大规模生产。

长川科技是国内领先的集成电路测试设备企业, Chiplet 芯粒的测试与先进封装将为公司带来新机遇。华峰测控是国内领 先的集成电路测试设备企业,同样受益于 Chiplet 芯粒测试与先进封装带来的机遇。

兴森科技是国内 IC 封装基板领先企业,在应用 Chiplet 技术的先进封 装材料领域有望持续拓展。华大九天Chiplet 技术的应用需要 EDA 工具 的全面支持,作为国内 EDA 龙头,有望在 Chiplet 领域进行拓展。

寒武纪2022年3月30日回复称思元370是寒武纪首款采用chiplet(芯粒)技术的AI芯片,采用7nm制程工艺,最大算力高达256TOPS(INT8),是寒武纪第二代产品思元270算力的2倍。

摩尔定律减缓带来了小芯片的设计需求,性能提升、成本降低以及大芯片的缺陷问题是 Chiplet 设计成为趋势的三大推动因素。

总体来看,Chiplet是后摩尔时代实现性能与成本突破的最优解,国外各大厂商持续布局。

根据研究机构 Omdia 报告,2024年采用Chiplet的处理器芯片的全球市场规模将达 58 亿美元,到 2035 年将达到570亿美元。

Chiplet作为目前受到广泛关注的新技术,给全球和中国的半导体市场带来了产业变革与机遇,降低了芯片设计门槛,带动IP设计厂商转换为Chiplet供应商,并且推动了先进封装、测试环节的需求。

来源于网络